티스토리 뷰

Verilog HDL를 주제로 한 두번째 포스팅에서 다룰내용은 BCD코드 입력을 디바이스의 SevenSegment에서 확인가능한 코드로 변환해주는 모듈의 구현입니다.

먼저 SevenSegment에 대한설명을 드리겠습니다.

세븐세그먼트는 우리 주변에서 흔히 볼수있는 숫자표현 디바이스입니다.

전자식 손목시계 또는 알람시계, 타이머 등등 여러 장비에서 확인이 가능한데요 사진을 보시면

아~ 이거~ 하시며 느낌이 오실것입니다.

위의 그림과 같이 생겼습니다.

오늘은 저번 포스팅에서 만든 BCD코드를 바로 이7-Segment를 통해 눈으로 확인해볼것입니다.

물론 코드는 BCD지만 눈에보이는 형식은 10진수처럼 보이게 말이죠 ㅎㅎ

거두절미하고 바로 설계과정 설명드리겠습니다.

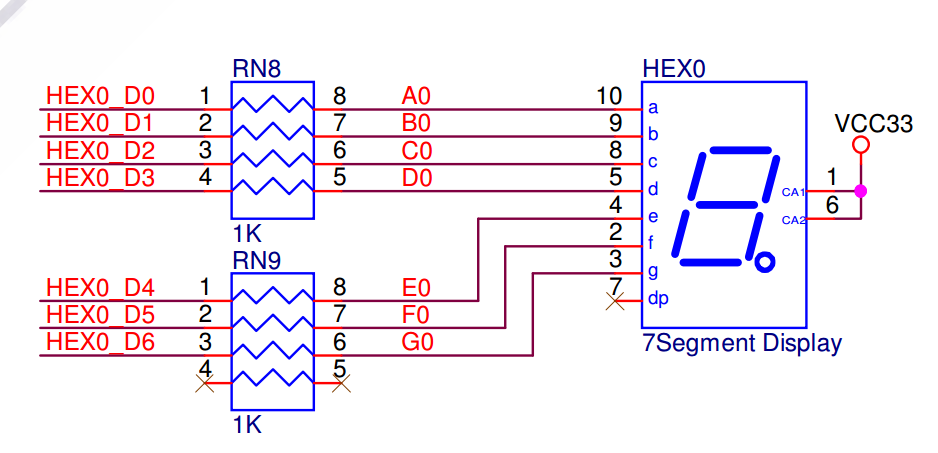

회로도를 먼저 살펴보겠습니다.

복잡해보이는 그림이지만 한가지만 확인하면 됩니다. 자세히 보시면 세븐세그먼트 디스플레이로 들어가는

숫자의 진행과 abcd 알파벳의 진행이 역순인것을 확인할수 있습니다. 이것을 참고로 나중에 핀을 어싸인해줄때

역순으로 연결해주시면 됩니다.

먼저 BCD코드로만든 4비트를 인풋으로 잡습니다.

그리고 세븐세그먼트의 조합논리회로 구성을 확인하신후 그 순서에 맞게 2진코드로 숫자를 분배해줍니다.

이런식으로 세븐세그먼트 신호는 순서가 있습니다 만약 0을 표현하고 싶다면 제일마지막의 g를 꺼줘야 하겠죠

저는 parameter 잡아서 ZERO = 7'b1000000로 설계하겠습니다.

왜 g가 제일 앞자리에 와서 1000000이냐구요? 회로도를 보시면 꺼꾸로 되있으니까요~

비슷한 원리로 0~9의 parameter를 선언해주시고 조건문안에 넣어 코딩을 마무리해주시면 아래와 같습니다.

Verilog HDL code)

module BCD_to_SevenSeg (input[3:0] BCD_in, output reg[7:0]DISPLAY);

//input leading_zero; first is 1,

parameter ZERO = 7'b1000000;

parameter ONE = 7'b1111001;

parameter TWO = 7'b0100100;

parameter THREE = 7'b0110000;

parameter FORE = 7'b0011001;

parameter FIVE = 7'b0010010;

parameter SIX = 7'b0000010;

parameter SEVEN = 7'b1011000;

parameter EIGHT = 7'b0000000;

parameter NINE = 7'b0010000;

parameter BLANK = 7'b1111111;

always @(BCD_in)

case(BCD_in)

0 : DISPLAY = ZERO;

1 : DISPLAY = ONE;

2 : DISPLAY = TWO;

3 : DISPLAY = THREE;

4 : DISPLAY = FORE;

5 : DISPLAY = FIVE;

6 : DISPLAY = SIX;

7 : DISPLAY = SEVEN;

8 : DISPLAY = EIGHT;

9 : DISPLAY = NINE;

default : DISPLAY = BLANK;

endcase

endmodule

마지막으로 이전 포스팅때 만든 Binary to BCD와 이번포스팅의 BCD to SevenSegment 모듈을 이용하여

디바이스에 출력해 결과를 확인해 보겠습니다.

DEMO)

'Language > Verilog HDL' 카테고리의 다른 글

| Verilog HDL - Clock Generator (1) | 2021.01.29 |

|---|---|

| Verilog HDL - Counter (0) | 2021.01.29 |

| Verilog HDL - Binary to BCD (1) | 2021.01.29 |

| Verilog HDL - Basic (2) | 2021.01.29 |

| Verilog HDL - intro (1) | 2021.01.29 |