티스토리 뷰

Verilog HDL - Digital Calendar_제안(Day calc module)

ShinyOcean 2021. 2. 6. 14:24Verilog HDL를 주제로 한 아홉번째 포스팅에서는 년,월,일을 카운팅하는 Year-Month-Day counter모듈에 이어

디지털 달력의 요일계산 모듈을 다루어 보겠습니다.

먼저 탑모듈의 회로도를 살펴보겠습니다.

우측 상단에 Day_calc라 정의해둔 모듈이 바로 요일계산 모듈입니다.

Day_calc모듈에서는 년,월,일의 값을 각값마다 분리하여 이진코드로 인풋을 취합니다.

만약 98년 10월 22일 이라면 98,10,22 이렇게 3개의 신호가 인풋으로 설정되는겁니다.

그리고 아웃풋으로 7개의 LED를 이용하여 요일을 표시하게됩니다.

예시는 다음과 같습니다.

<일요일>

일 월 화 수 목 금 토

■ □ □ □ □ □ □

<월요일>

일 월 화 수 목 금 토

□ ■ □ □ □ □ □

<화요일>

일 월 화 수 목 금 토

□ □ ■ □ □ □ □

...

...

...

<토요일>

일 월 화 수 목 금 토

□ □ □ □ □ □ ■

요일의 구분은 위와 같이 LED의 위치를 이용하여 각 요일을 표시하는 방법으로 채택하였습니다.

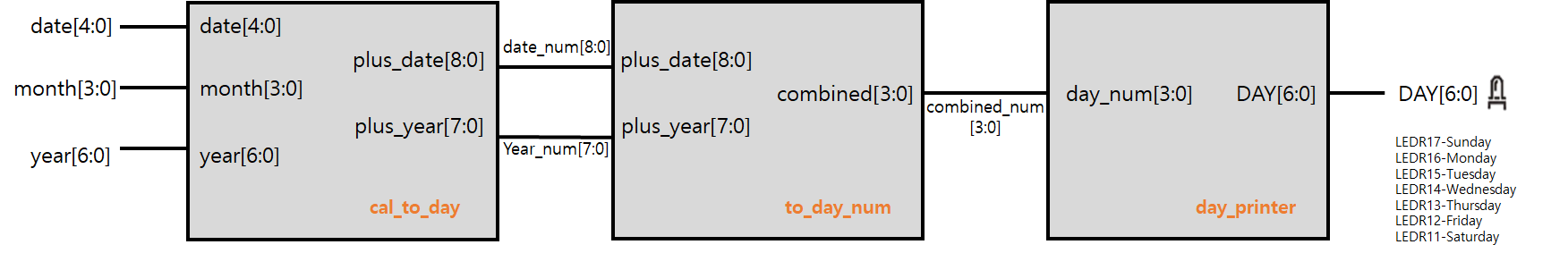

다음은 회로도를 살펴 보겠습니다. 프로젝트 제안 과정에서의 요일계산모듈 내부회로도는 아래의 그림과 같습니다.

위그림에서의 회로의 흐름을 말씀드리겠습니다.

먼저 2진코드로 년,월,일 값을 cal_to_day모듈의 인풋으로 취합니다.

그러면 기준일로 세운 값에서 부터 차일을 계산하여 to_day_num모듈로 보내주고 to_day_num모듈에서

0부터6까지의 7가지 숫자로 모든 케이스를 분류합니다.

이때 인풋으로 들어온 날짜에 알맞은 요일의 숫자 케이스로 변환되는 것 입니다.

마지막으로 day_printer모듈을 이용하여 각 케이스의 숫자를 LED에 표현가능한 신호로 변환하여 아웃풋을 취합니다.

프로젝트의 제안과정에서는 간단하게 방향성만 제시 해두고 중간과정이나 최종과정에서 상세히 풀어나가겠습니다.

'Language > Verilog HDL' 카테고리의 다른 글

| Verilog HDL - Digital Calendar_제안(Mux, Demux) (0) | 2021.02.06 |

|---|---|

| Verilog HDL - Digital Calendar_제안(D-Day module) (0) | 2021.02.06 |

| Verilog HDL - Digital Calendar_제안 (Year Mon Day module) (0) | 2021.02.03 |

| Verilog HDL - Digital_clock(am/pm) (1) | 2021.02.03 |

| Verilog HDL - Digital_clock(basic) (0) | 2021.02.01 |