티스토리 뷰

Verilog HDL를 주제로 한 열한번째 포스팅에서는 Mux, Demux 모듈을 다루어 보겠습니다.

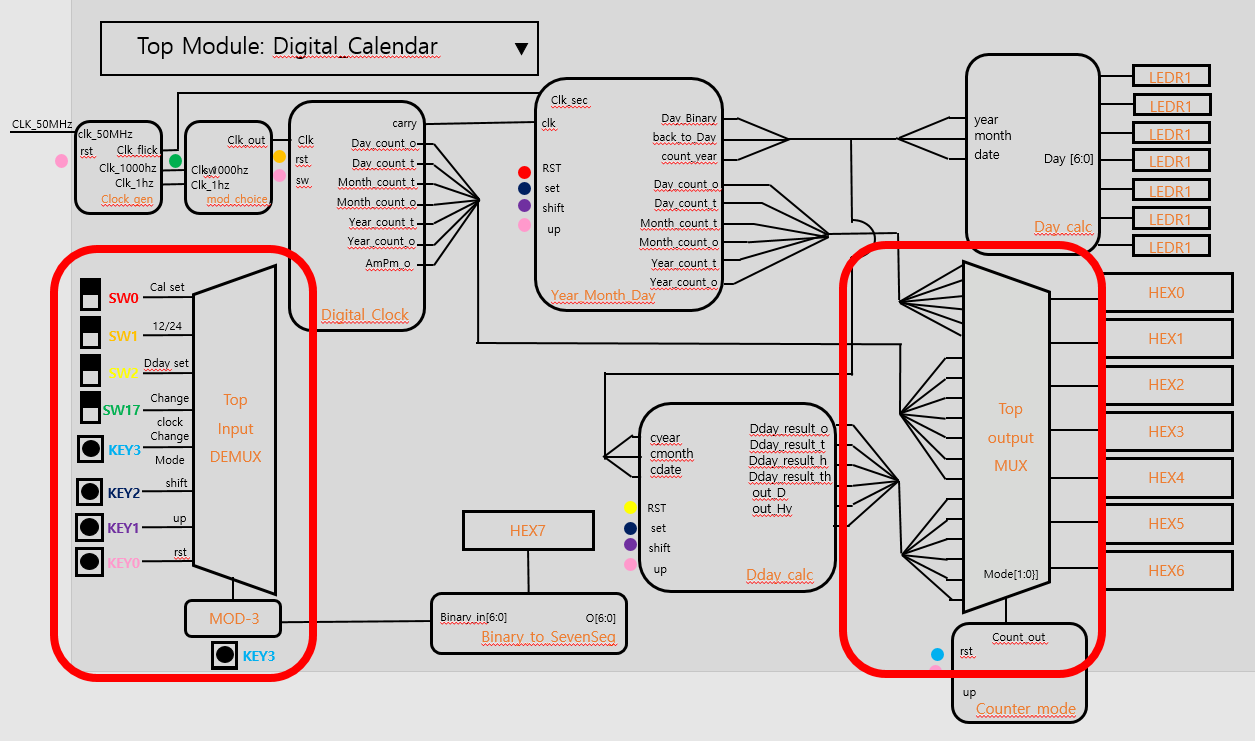

다음의 그림에서는 Top모듈에서 mux와 Demux를 붉은 영역으로 표시해두었습니다.

먼저 Mux에 대해 다루어 보겠습니다.

먹스는 여러개의 인풋신호중에 몇몇개의 신호만 clk에 따라 아웃풋신호로 나오는 모듈입니다.

만약 세븐세그먼트가 두개라고 가정해보겠습니다.

그런데 만약 2개의 7-세그먼트보다 많은 양의 신호를 가지고 있을때는 어떻게 할까요

시계의 경우 시와 분이 있는데 7-세그먼트 2개로는 둘을 표현하지 못하지요 이럴때 사용하는 것이 Mux입니다.

먹스를 사용하여 clk를 기준으로 0일때는 두개의 세븐시그먼트에 시를 표시하고 1일때는 분을 표시한다면

제한된 갯수의 7세그먼트를 이용하더라도 시와 분을 둘다 표현할수 있을것입니다.

이처럼 다수의 입력에서 소수의 출력으로 가는 선발의 기능을 수행하는 것은 먹스입니다.

그렇다면 Demux는 어떠한 역할을 수행할까요?

디먹스는 몇몇의 인풋신호를 clk에 따라 다수의 아웃풋신호로 나오는 모듈입니다.

먹스의 경우에는 다수의 신호를 제한된 디바이스로 표현해야 할때 탁월하게 사용되었습니다.

디먹스의 경우에는 어떨까요? 이전 포스팅에서 사용된것과 같이 제한된 디바이스로 다수의 신호를

표현해야 할때 탁월합니다.

이번에도 예시를 들어보겠습니다.

만약 스위치는 하나인데 이를 이용하여 방에 불도 켜야하고 데스크탑에 전원도 켜야 하는 상황이 있다

가정해 보겠습니다. 그렇다면 이 스위치를 이용하여 방 불만 켜거다 데스크탑만 켜야 할때는 어떻게 할까요

하나의 스위치로는 둘을 따로 조종할수 없겠죠 이때 사용하는 것이 Demux입니다.

디먹스를 사용하여 clk를 기준으로 0일때는 방불의 스위치역할을 하게 1일때는 데스크탑의 전원스위치가

되게 하는것이죠. 이렇게 하면 제한된 디바이스로 많은 신호를 다룰수 있을것입니다.

이처럼 소수의 입력에서 갈수 있는 다수의 출력중에 클럭에 따른 분류의 기능을 수행하는 것은 디먹스입니다.

'Language > Verilog HDL' 카테고리의 다른 글

| Verilog HDL - Digital Calendar_보완(Day calc module) (1) | 2021.02.06 |

|---|---|

| Verilog HDL - Digital Calendar_보완(Year Mon Day module) (0) | 2021.02.06 |

| Verilog HDL - Digital Calendar_제안(D-Day module) (0) | 2021.02.06 |

| Verilog HDL - Digital Calendar_제안(Day calc module) (0) | 2021.02.06 |

| Verilog HDL - Digital Calendar_제안 (Year Mon Day module) (0) | 2021.02.03 |