티스토리 뷰

Verilog HDL - Digital Calendar_보완(Year Mon Day module)

ShinyOcean 2021. 2. 6. 16:21Verilog HDL를 주제로 한 열두번째 포스팅에부터는 제안설계때의 문제점을 보완하고 설계의 완성도를높여가며 프로젝트를 진행하겠습니다.

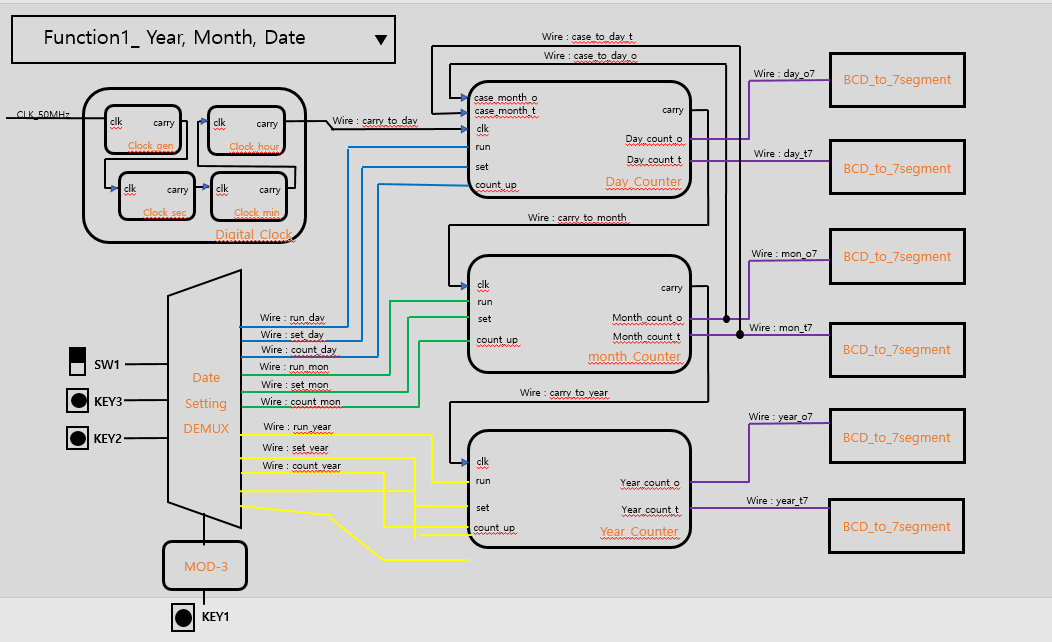

이번 포스팅에서 완성할 계획인 모듈은 날짜의 카운팅을 담당하는 Year Mon Day module입니다.

먼저 설계제안의 과정까지를 리뷰 하겠습니다.

제안설계 때의 회로도를 먼저 살펴 보겠습니다.

설계제안 과정에는 윤년에 따른 2월 말일에 대한 카운팅과 날짜의 셋팅과정에 대한 내용이 부실하였습니다.

이번 포스팅에서는 날짜 셋팅을 위한 입력키의 분배에 대한 내용을 세심하게 다룰것 입니다.

그리고 윤년에 따른 2월의 다른 말일을 카운팅하는 설계 또한 보완하여 프로그래밍 과정에서 오류가 없는

모듈을 완성해 보겠습니다.

먼저 기존의 문제들과 개선되거나 추가되었으면 하는 부분들을 정리하여보겠습니다.

1. Year, month, Day각 카운터의 output을 10의 자리와 1의자리를 분리한 방식의 문제점 개선

먼저 output의 배출 방식을 10진수 각자리수 마다를 분리하여 배출하려했던 이유를 말씀드리겠습니다.

이전 포스팅에서 다룬 2진수를 디바이스의 7-segment에 10진수로 표기 하기 위하여 취했던 방식은 Binary_to_BCD 모듈을 이용하여

Binary code를 BCD code로 변환하고 BCD code를 다시 7-segment에 표현가능한 신호로 변환하는 BCD_to_Sevenseg모듈을 이용하여

최종적으로 결과를 추출하는것 이었습니다.

하지만 생각을 조금 달리하여 2진수의 범위를 각 자리수마다 잘라내어 0부터 9까지의 신호로 아웃풋을 만든다면 어떻게 될까요?

중간에 BCD코드로 만드는 모듈을 사용하는 과정이 생략되어도 상관없게 됩니다. 0~9의 2진수 코드가 바로 BCD code이기 때문이죠

이렇게되면 어싸인하는 모듈의 양을 줄일수 있게 되어 더욱 유용한 설계가 될것이라 생각했었습니다.

하지만 나중에 더 복잡한 과정을 초래하게 되었습니다. 바로 윤년과 각달의 말일을 계산하는 과정에서 Feedback시켜야 하는 신호가

BCD코드값의 범위를 훌쩍 넘기기 때문이죠 만약 98년을 year_case로 넘길경우도 와이어와 인풋 아웃풋의 선언이 번거로워 지기 때문

입니다 그래서 저는 Feedback신호의 범위를 고려하여 아웃풋의 범위를 10진수 2자릿수를 표현할수 있도록 7비트로 선언하였습니다.

2. 윤년을 고려한 Year카운터로 부터의 Feedback 신호 구축

윤년을 고려하는 Feedback신호를 구축하기위해 month 카운터에 취했던 방식과 동일하게 4의 배수년도의 4로나눈 나머지값이 0일때

즉 윤년일경우 yoon이라는 신호를 긍정(true)로 바꾸는 boolean기법을 사용하였습니다. 이는 나중에 프로그래밍 과정에서 기술하겠습 니다.

3. 날짜 셋팅시 set스위치를 이용한 셋팅모드 진입

날짜 셋팅을 하기위하여 여러 방법을 구상하고 있었습니다. 그러다가 기본적으로 Digital_Clock의 hour_counter의 carry값을 clk으로

취한 날짜 카운터가 셋팅시 시간이 계속 증가되지 않게 하려면 clk을 잠시 취하지 않을 필요가 있었습니다.

이를 위하여 always문을 사용하여 토글스위치와 엮어주는 것이었습니다. 스위치가 올라 갈경우 clk의 값으로 count가 up되는것이 아닌

push 버튼이 눌릴때 up될수 있도록 설계하는 것입니다.

4. 날짜 셋팅시 flikering 모듈을 통한 현재 셋팅하고 있는 카운터의 위치를 알림

날짜 셋팅할때 set up - Day count up - shift - Month count up - shift - Year count up - set down

의 로직을 구상했었습니다. 그런데 이때 shift 의 경우 버튼이 눌려 다음 카운터의 위치로 버튼이 어싸인 된지 어떻게 확인할까를

고민하게 되었습니다. 방법은 시중에 판매하고 있는 전자 달력, 또는 전자 시계와 같이 현재 셋팅중인 위치를 깜빡임을 통하여

분별하는 것이었습니다.

위의 문제점 또는 개선사항들을 반영하여 구상한 최종 회로도는 다음과 같습니다.

flikering모듈에 대해서만 다루어 보겠습니다. 나머지 모듈들은 문제점 및 개선사항을 언급한 윗부분에서와 동일하게

설계를 완료하였습니다.

flikering모듈은 감빡임의 신호를 분배하여 주기위하여 선언해주었습니다. 먼저 4Hz의 진동수를 이용한 2진 신호를

flikering모듈을 통하여 생성하고 디먹스의 인풋으로 넣어주었습니다. 디먹스를 통해 어떤 카운터에 키를 분배할까를

정하는 동시에 해당 카운터에 키가 지정되었을때, flik신호를 해당 카운터의 Binary_to_7segment모듈의 출력에 영향을

줄수 있도록 지정해주었습니다.

만약 디먹스의 클럭에 따라 Month카운터의 날짜를 셋팅하고 있다면 Month카운터의 아웃풋이 연결된

Binary_to_7segment 모듈의 아웃풋 신호를 flik신호에 따라 조정되게하였습니다.

flik신호가 0이라면 값을 표기 하고 flik신호 1이라면 Blank를 표기하여 눈으로 볼땐 깜빡일수 있도록 지정하였습니다.

'Language > Verilog HDL' 카테고리의 다른 글

| Verilog HDL - Digital Calendar_보완(D-Day module) (0) | 2021.02.09 |

|---|---|

| Verilog HDL - Digital Calendar_보완(Day calc module) (1) | 2021.02.06 |

| Verilog HDL - Digital Calendar_제안(Mux, Demux) (0) | 2021.02.06 |

| Verilog HDL - Digital Calendar_제안(D-Day module) (0) | 2021.02.06 |

| Verilog HDL - Digital Calendar_제안(Day calc module) (0) | 2021.02.06 |