티스토리 뷰

Verilog HDL를 주제로 한 열네번째 포스팅은 D-Day module에 대한 계산과정 디테일을 리뷰하고

보완설계를 완성해보겠습니다.

먼저 최종적인 인터페이스는 다음과 같습니다.

최종적으로 세븐세그먼트 6개를 이용하여 D-Day에 대한 count를 표시하였습니다.

D-Day module모듈의 설계제안 과정에서는 디먹스를 이용한 타겟 날짜의 셋팅을 고안하였습니다.

그리고 Year_Month_Day 모듈의 아웃풋인 현재 날짜와의 합차연산으로 구한 D-Day값을 세븐세그먼트를 통해

출력하기로 하였습니다.

타겟날짜의 셋팅과정속에서 push버튼을 이용하여 count up을 할수있는 카운터 3개를 어싸인하고,

디먹스를 이용하여 push버튼의 신호를 3개의 카운터에 분배해줄 계획을 세웠습니다.

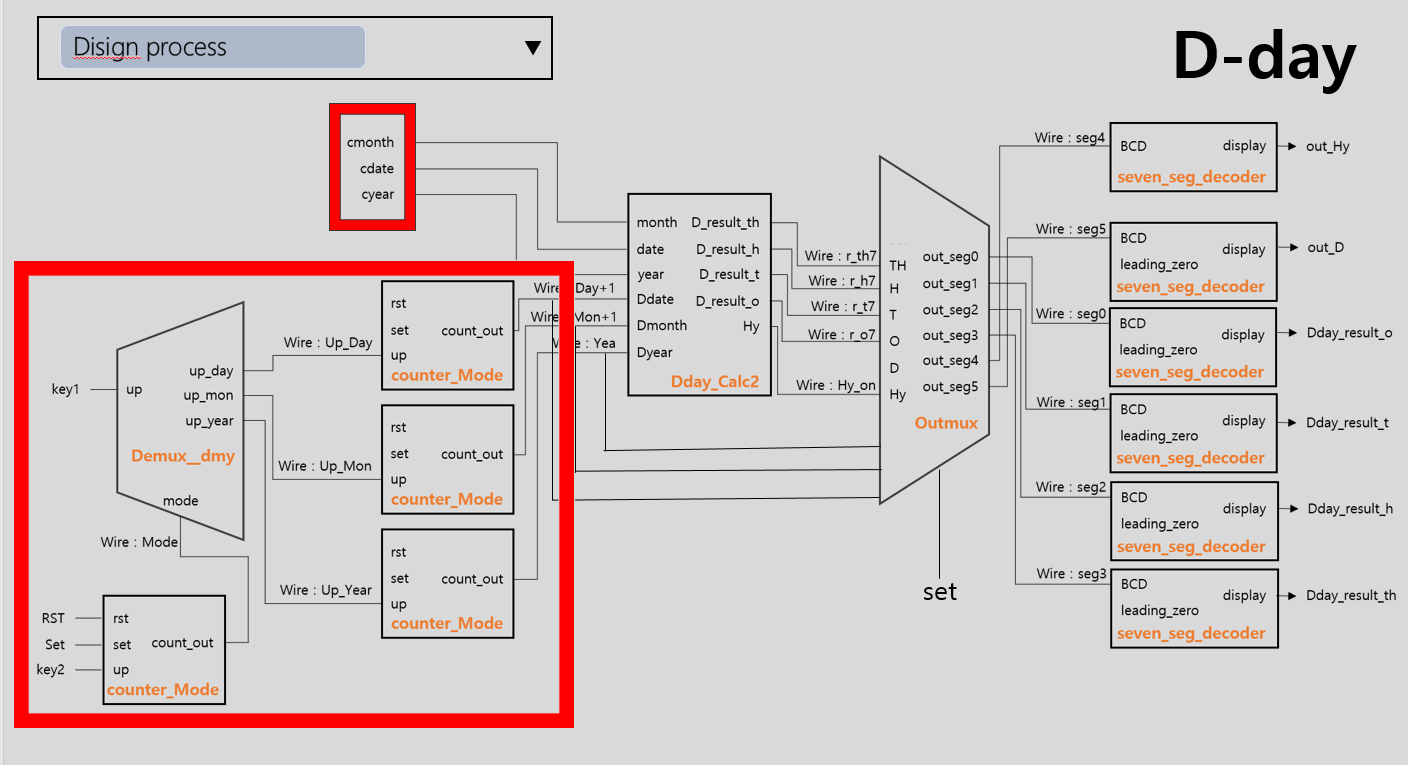

이과정을 종합한 최종 회로는 아래와 같습니다.

메인이 되는 D-day calc 모듈은 중앙에 배치하였습니다. 이를 기준으로 좌측에 붉은 박스로 표시한 두 영역이 D-day로

타겟팅할 날짜를 셋팅하기 위한 모듈의 아웃풋 날짜 값과 Year_Month_Day모듈의 아웃풋인 현재 날짜 값입니다.

좌측 하단의 큰 박스 먼저 살펴 보겠습니다.

먼저 count up에 사용되는 push버튼은 key1단 하나 입니다. 이 하나의 버튼을 mod - 3 counter의 count out값으로 클럭을 잡아 shift할수 있도록 설계해 보았습니다.

그리고 Day와 Month카운터의 우측 아웃풋을 살펴보면 와이어를 통해 인풋으로 다시 들어가는 과정 중에 +1을 해주었습니다. 이는 일과 월의 값에 0이 없기때문입니다. 0월 1일 이나 1월 0일이 없는것 과 같죠.

그후 D-day calc모듈을 통하여 6개의 아웃풋 신호로 변환시켰습니다 D, -, 1000자리, 100자리, 10자리, 1자리 순입니다.

이는 아웃풋 먹스를 통하여 set신호가 들어오지 않는다면 계산된 D-day의 값을, 신호가 들어온다면 타겟으로 설정할 날짜값을 출력 합니다.

set신호를 올려 날짜가 출력될때는 count를 push버튼으로 조작하여 날짜를 셋팅하고 set신호가 내려간다면

현재 날짜와 타켓날짜의 차이만큼인 D-day count값을 세븐세그먼트에 출력하는 것입니다.

'Language > Verilog HDL' 카테고리의 다른 글

| Verilog HDL - Digital Calendar_최종 데모(Final Demo) (0) | 2021.02.10 |

|---|---|

| Verilog HDL - Digital Calendar_보완(Final Top module) (0) | 2021.02.09 |

| Verilog HDL - Digital Calendar_보완(Day calc module) (1) | 2021.02.06 |

| Verilog HDL - Digital Calendar_보완(Year Mon Day module) (0) | 2021.02.06 |

| Verilog HDL - Digital Calendar_제안(Mux, Demux) (0) | 2021.02.06 |